ARM 教材 - cortex-m - 1 - instruction set architecture

Index : ARM cotex-M study

Thumb - 16 bit

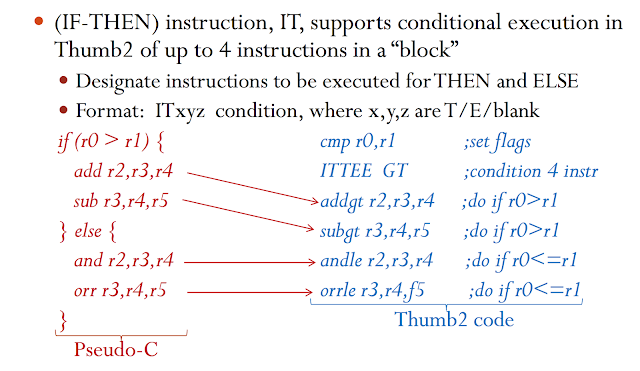

Thumb2 - 32 bit

Thumb 比 Thumb2 有更好的 code density

Thumb2 比 Thumb 有更好的 執行效能

Instruction Set, 可分為幾類

1. Data Processing

- Arithmetic

- Logic

- Comparison

- Multiply

2. Data Movement (memory access)

Ref: C/C++11 mapping to processor

* load acquire register

* store release register

B : byte, H : half-word

ARM v8 : LDA/STL

3. Flow control

Ref: http://www.eng.auburn.edu/~nelson/courses/elec5260_6260/slides/Chapter2%20ARM.pdf

4. DSP

- cortex-m4 DSP

saturating arithmetic

SIMD

5. FPU

IEEE754

--

Ref: ARM M-profile

variant of the T32 instruction set.

--

Ref: C/C++11 mapping to processor

spinlock - arm v7m

Lock acquire (address of the lock is in r1, the value of taken lock is in r0):

Loop:

LDREX R5, [R1] ; read lock

CMP R5, #0 ; check if 0

WFENE ; sleep if the lock is held

STREXEQ R5, R0, [R1] ; attempt to store new value

CMPEQ R5, #0 ; test if store suceeded

BNE Loop ; retry if not

DMB ISH ; ensures that all subsequent accesses are observed after the

; gaining of the lock is observed

; loads and stores in the critical region can now be performed

Lock release (r1 contains the address of the lock structure):

MOV R0, #0

DMB ISH ; ensure all previous accesses are observed before the lock is

; cleared

STR R0, [R1] ; clear the lock.

--

--

Hackpad

下一篇 : Data Processing

留言

張貼留言